山本ワールド

降圧コンバーターの製作

回路図

仕様

入力 2.8~6V程度

出力 1.4V 0.2A程度

スイッチング周波数 f=20KHz以上(コアがうなっても音が聞こえないように)

最低限確保する効率 50%以上(抵抗で電圧をドロップさせる仕様よりは最低限効率が良くなければ意味がない)とし手持ちの部品を採用、時間があれば低VCE(sat)のトランジスタやショットキーダイオード等を使用して効率アップする。

回路構成

スイッチングレギュレータ用ICであるTL497や秋月通商のキット等が候補にあがったが、出力電圧が低いこと、動作の確認には個別のICやトランジスタで作成したほうが良いと思い、タイマーIC555でPNPトランジスタによりスイッチングする降圧コンバータとした。NPNの方がトランジスタの選択肢が多いのだがベース電圧が電源電圧以上高くできないため、必然的にエミッタ電圧が電源-0.6V程度となり、スイッチング時0.6Vの損失が発生する。実際にはドライブ回路が電源電圧までスイングできないためさらに発生する。PNPの場合、ベース電圧は電源電圧より低くてかまわないため、このような制約は発生しない。(三端子レギュレータの通常タイプ78xxはNPNトランジスタを出力に使用しているため同様に損失が多い。低損失タイプはPNPを使用している。)

555がLOWの時(OUT端子に電流が吸い込まれる。)トランジスタがOnとなる。HIの時(OUT端子から電流が流れ出す。)はトランジスタがOffとなる。555はドライブ電流が大きく取れるので良く見られるNPN+PNPという構成にはしなかった。

設計

出力電圧はトランジスタがOnとなっている時間の比率で決まる。(負荷が重いとき)

2.8v/1.4v=2

最大デューティ 1/2=50%

Toff=1/f*0.5=25μs f=20kHz

I=V/L*t

L=V/I*t=2.8/0.4*25e-6=234μH

ILmax=Iout+Vout/(2L)*TOff=0.2+1.4/(2*234e-6)*25e-6=0.275A

ΔI=1.4/(2*117e-6)*25e-6=0.075A

| L | 220μH | 150μH | 100μH | 80μH | |

| 1/2t | f(kHz) | 12.7 | 18.5 | 28 | 35 |

| t= | 0.625 | 0.625 | 0.625 | 0.625 | |

| t | Toff=ΔI/Vout*2*L(μs) | 23.5μs | 16.1μs | 10.7μs | 8.6μs |

| 1/(2t) | 21.2kHz | 31.1Khz | 47.7KHz | 58.3kHz |

555の発振周期は仮に50%デューティ比と仮定すると

RA=1kΩとすると RB=11k C=0.002 f=31.3kHz VH=16.63 VL=15.25

RA=2.2 RB=22k C=0.001μf=31.2kHz VH=16.77 VL=15.25

RA=4.7k RB=27k C=470pF f=31.1kHz VH=16.84 VL=15.31

の組み合わせとなる。(タイマーIC555を利用した回路の設計で計算)手持ちのコンデンサの関係で真ん中のケースを採用

トランジスタはとりあえず手持ちの2SB686を使用する。

IC=0.5Aの時 IB=10mA 、VBE=0.6Vと仮定、2.8-0.6=2.2V ベースエミッタ間放電促進用に100Ω

IRB=0.6V/100Ω=6mA 555のIout=10+6=16mA 2.2/16mA=約100Ω

出力電圧の安定化

当初の試作回路では、トランジスタのコレクタをCONT端子につないでいた。電圧が高い場合は、トランジスタがOnとなり555のCONT端子の電圧を下げて、発振周波数を上げてトランジスタのOn時間を短くして電流供給時間を短くして出力電圧を下げる回路としたが、試作するとCONT端子が0Vとなり、555の出力がLOWでホールドされトランジスタがOnのままとなった。CONT端子の入力電圧範囲は、電源電圧の半分ちょっと上から電源電圧の2/3程度までである。意外と制御できる範囲は狭い。CONT端子の入力電圧が規格より小さい場合の動作は保証されておらず内部のコンパレータが正常に動作するとは限らない、試作した回路では、OUT端子がLOW状態に保持された。したがって、トランジスタはOnのままとなりほぼ電源電圧と同じ電圧が出力側に発生した。

改良型では、CONT端子ではなくTRIGGER端子に接続した。出力電圧が上がるとトランジスタがOnとなりTRIGGER端子をGND側に引っ張り555内部のフリップフロップ(FF)をセットする。したがってOUT端子がHiとなりトランジスタはOffとなる。このトランジスタのTRIGGER端子によりフリップフロップ(FF)をセットするまで電圧を下げられない場合、出力電圧の増加とともに、555がHIの時間は、Cへの充電が遅くなるので長くなり、555がLOWの時間はCの放電が速くなるので短くなる。したがって、出力電圧の増加とともにトランジスタがOnになる比率は少なくなる。

各部の電圧の観測

|

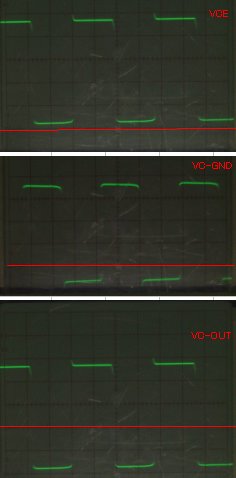

エミッタ・コレクタ間の電圧

電圧が低いときがトランジスタがOnとなりコイルに充電されている状態である。 VCE(sat)は0.3V程度である。 |

|

コイルの片方(コレクタ側)とGND間の電圧

正電圧の時は充電中、負の電圧の時は放電状態である。 充電中と放電中では+,-が逆になる。負の電圧は、ダイオードのアノード側がGNDにつながれているため、約0.6Vの電圧が生じている。充電期間が18μs、放電時間が19μsである。 |

|

|

コイルの両端の電圧(出力側をオシロのGNDに接続)

正の電圧の時充電、負の電圧の時は放電状態である。充電時は、ほぼ電源電圧-出力電圧が発生。放電時は出力電圧は-(出力電圧+ダイオードの順方向電圧)である。 |

入力が4.01V 0.098Aの時、出力が1.4V 0.175Aであった。効率は62%であった。出力特性は、下表のとおり。(電池が消耗して効率測定時より電圧が下がっている)

| V | A |

| 1.428 | 0.079 |

| 1.400 | 0.140 |

| 1.362 | 0.170 |

| 1.050 | 0.236 |